# AMDZ

# **PYNQ for HPC**

Graham Schelle Fellow, Adaptive and Embedded Computing Group (AECG)

### Agenda

Why Productivity Software for H<sup>2</sup>RC?

...a Machine Learning example (DPU-PYNQ) ...a Cloud example (PYXRT) ...a Quantum example (QICK)

And what about Productivity Software <u>for Hardware</u>? ....PYNQ-Metadata

#### Why Productivity Software for H<sup>2</sup>RC?

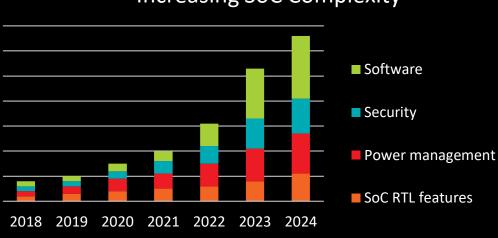

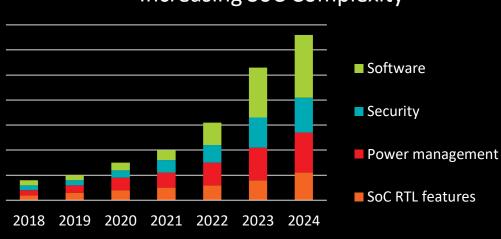

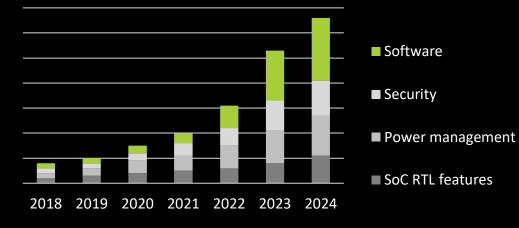

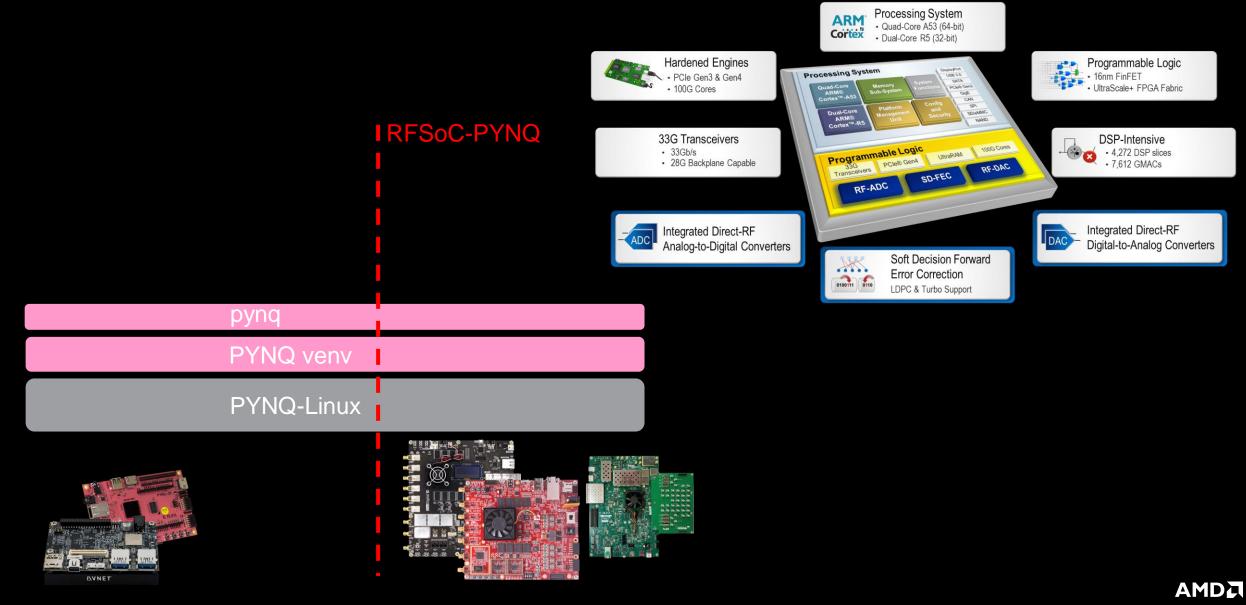

Increasing SoC Complexity

H<sup>2</sup> : Heterogeneous and High Performance

How can productivity software help here?

#### Why Productivity Software for H<sup>2</sup>RC?

Increasing SoC Complexity

H<sup>2</sup> : Heterogeneous and High Performance

Hardware complexity often exposed to software

...to enable user programmability

→ Software productivity challenges (and opportunities!)

#### Why Productivity Software for H<sup>2</sup>RC?

#### Increasing SoC Complexity

# Sity Glue It All Together With Python

Python is an advanced scripting language that is being used successfully to glue together large software components. It spans multiple platforms, middleware products, and application domains. Python is an object-oriented language with high-level data structures, dynamic typing, and dynamic binding. Python has been around since 1991, and has a very active user community. For more information, see the Python website http://www.python.org.

What is the "it" in this talk?

#### Guido van Rossum, 1998

# Example – DPU-PYNQ

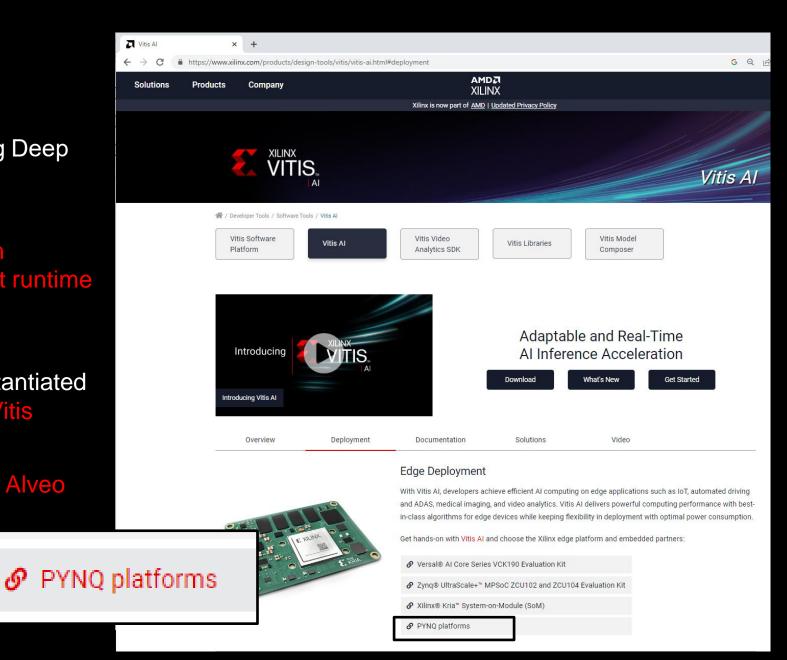

The DPU is AMD's Adaptive Computing Deep Learning Accelerator

Leverages a host-machine quantization framework for training and then a target runtime framework for execution

Its an IP block found within Vivado, instantiated within VitisAI, user software written in Vitis

Deployed on Zynq UltraScale, Versal & Alveo

####

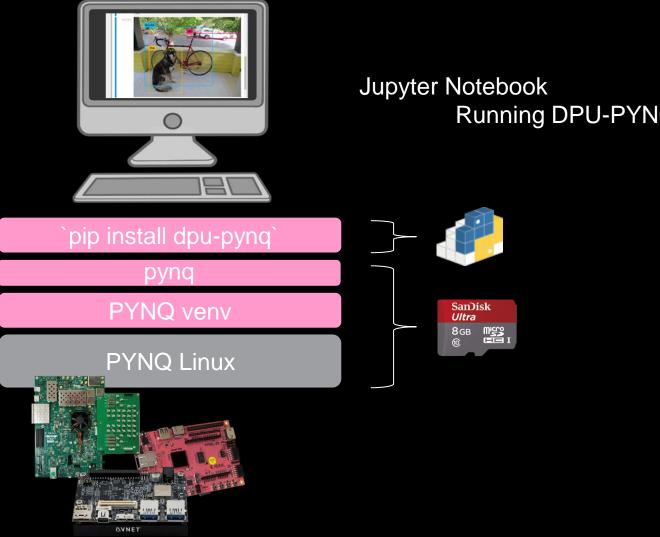

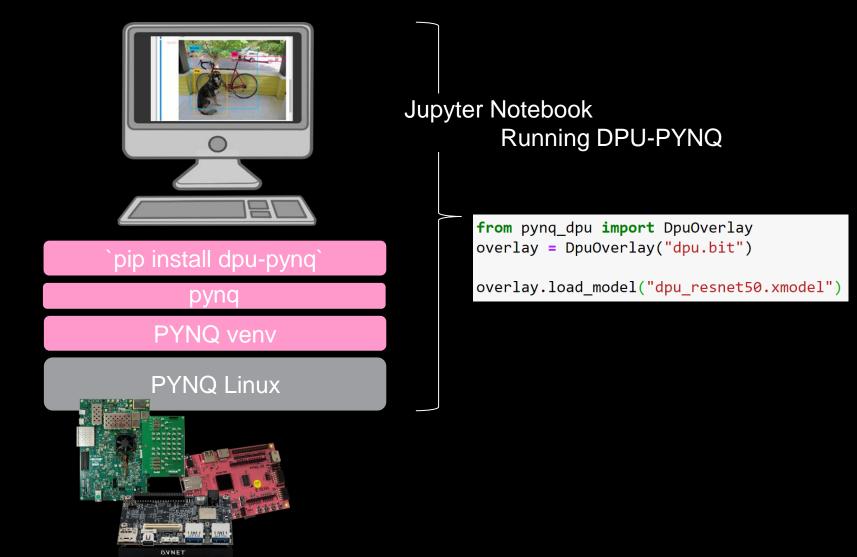

#### Jupyter Notebook Running DPU-PYNQ

# Running DPU-PYNQ

PYNQ v3.0 is now available. We've added pynq-metadata with support for hardware design introspection, more supported boards like the **#zcu208** and we continue to actively maintain PYNQ-Linux with upgraded software packages.

| PYNQ v3.0 (Belfast) Release     |         |             |                         |  |

|---------------------------------|---------|-------------|-------------------------|--|

| discuss.pynq.io • 1 min read    |         |             |                         |  |

| ੴੴ& Jeff Fifield and 202 others |         |             | 11 comments • 7 reposts |  |

| 🖒 Like                          | Comment | င့်) Repost | Send Send               |  |

| 11,213 impressions              |         |             | View analytics          |  |

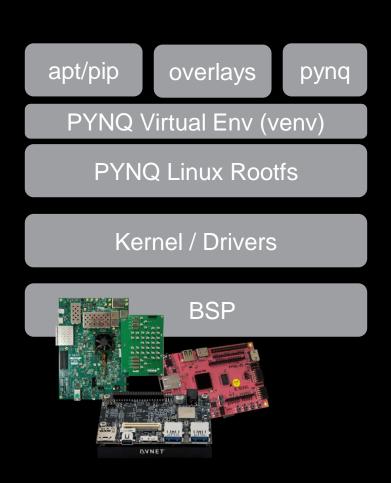

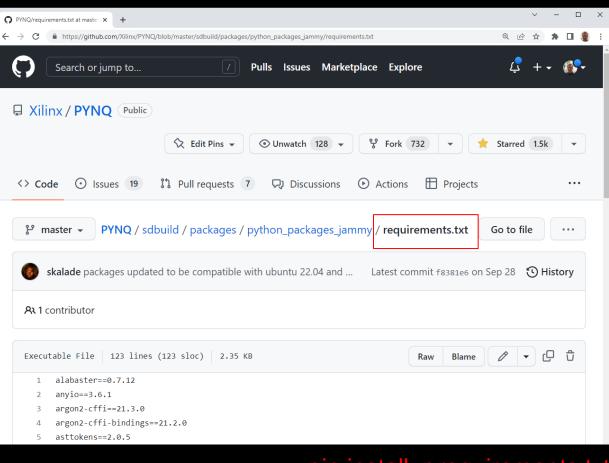

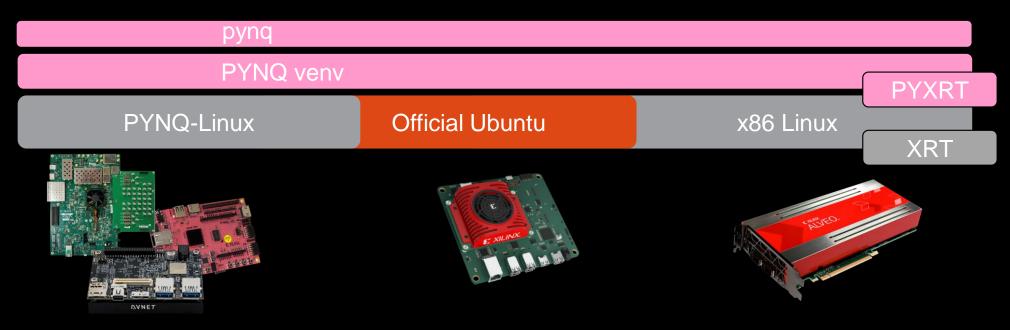

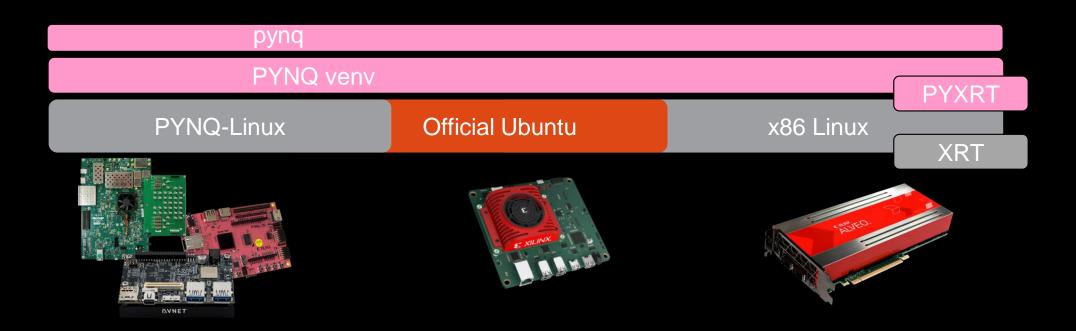

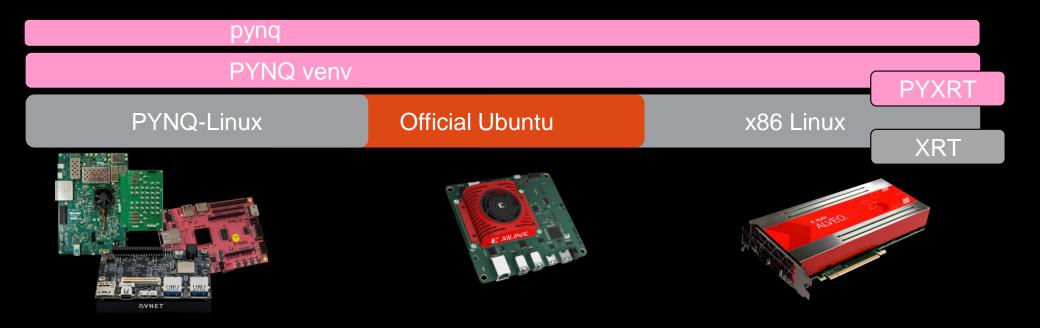

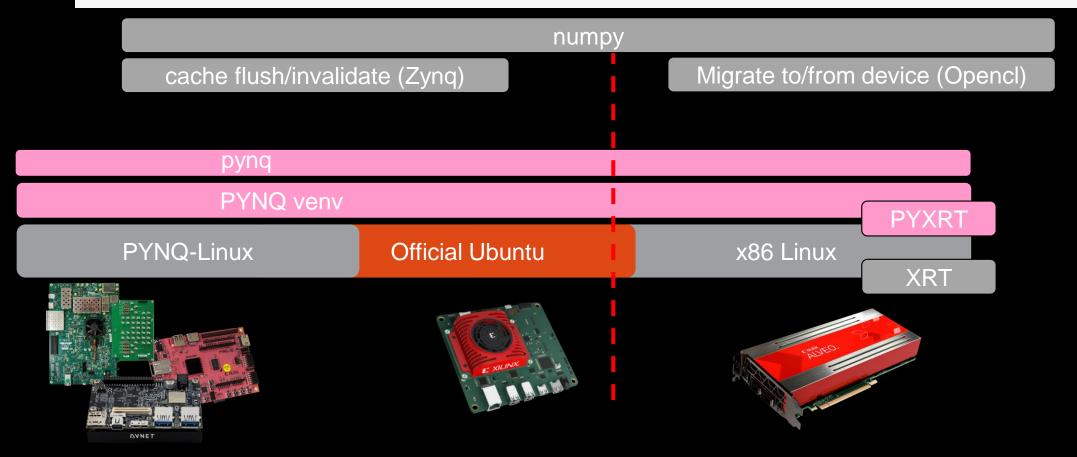

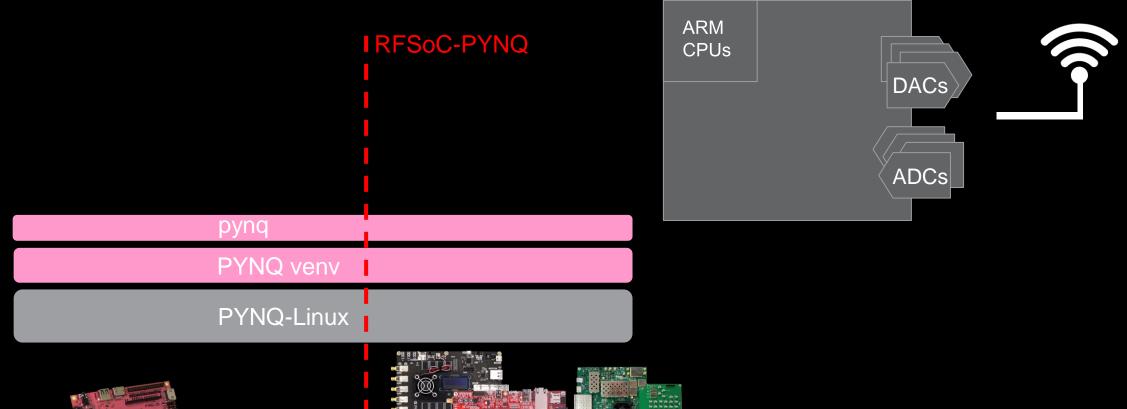

pynq PYNQ venv

#### PYNQ Linux

pip install -r requirements.txt pip install pynq

#### PYNQ Linux

# which platforms to build the [neural] networks for zynq\_platforms = ["ZCU102", "ZCU104"] alveo\_platforms = ["U250"] platforms\_to\_build = zynq\_platforms + alveo\_platforms

☐ Xilinx / finn-examples Public

```

ol = Overlay("an_example.xclbin")

```

ol = Overlay("an\_example.xsa")

ol = Overlay("an\_example.bit", dtbo="a\_devicetreeoverlay.dtbo")

#### PyLog: An Algorithm-Centric Python-Based FPGA Programming and Synthesis Flow

Sitao Huang<sup>10</sup>, Kun Wu, Hyunmin Jeong, Chengyue Wang, Deming Chen<sup>10</sup>, *Fellow, IEEE*, and Wen-Mei Hwu<sup>10</sup>, *Fellow, IEEE*  PyLog runtime uses PYNQ [20] and XRT, which are runtime libraries from Xilinx. The lower half of Fig. 2 shows an example of PCIe-based FPGA platform. Note that PyLog can support both PCIe-based highperformance FPGAs and low-power SoCs and MPSoCs

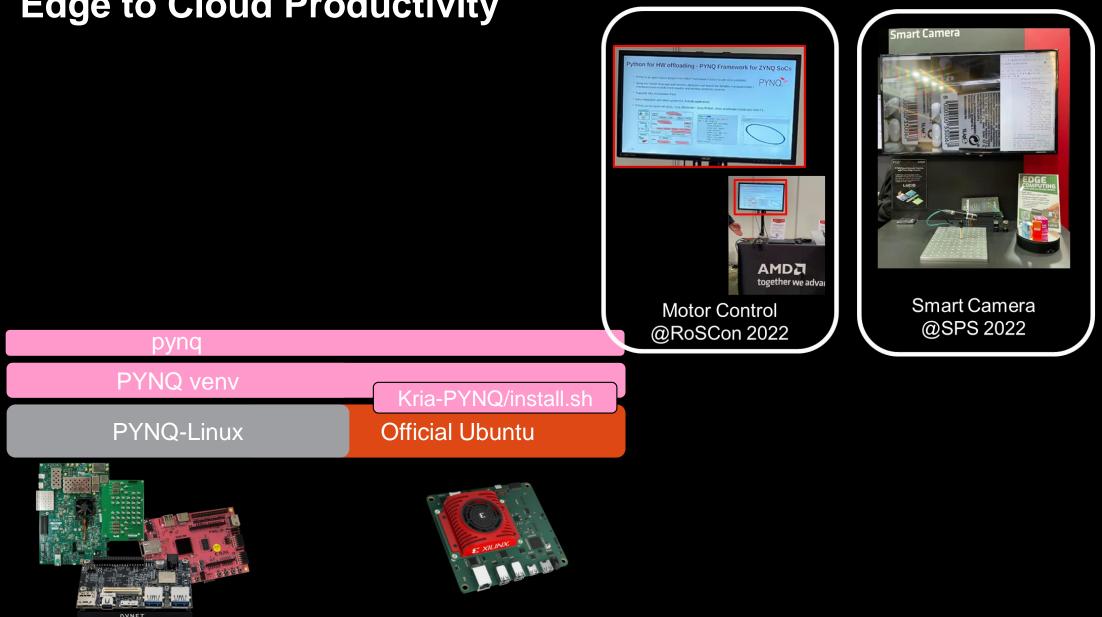

Unified edge to cloud API for adaptive computing

buffer = pynq.allocate(shape=(height, width, 3), dtype=np.uint8)

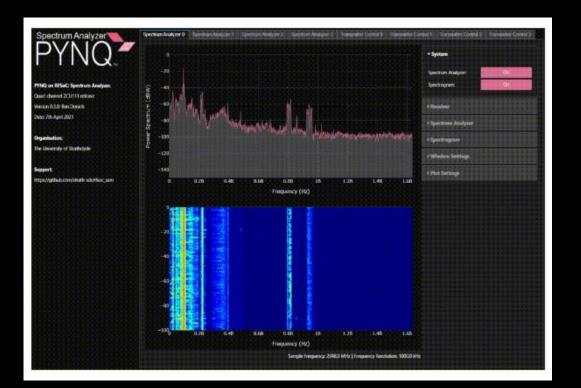

| 🛱 strath-sdr / <b>rfsoc_sam</b> ( | Public |

|-----------------------------------|--------|

|-----------------------------------|--------|

A Xilinx / DSP-PYNQ Public

☐ Xilinx / SDFEC-PYNQ Public

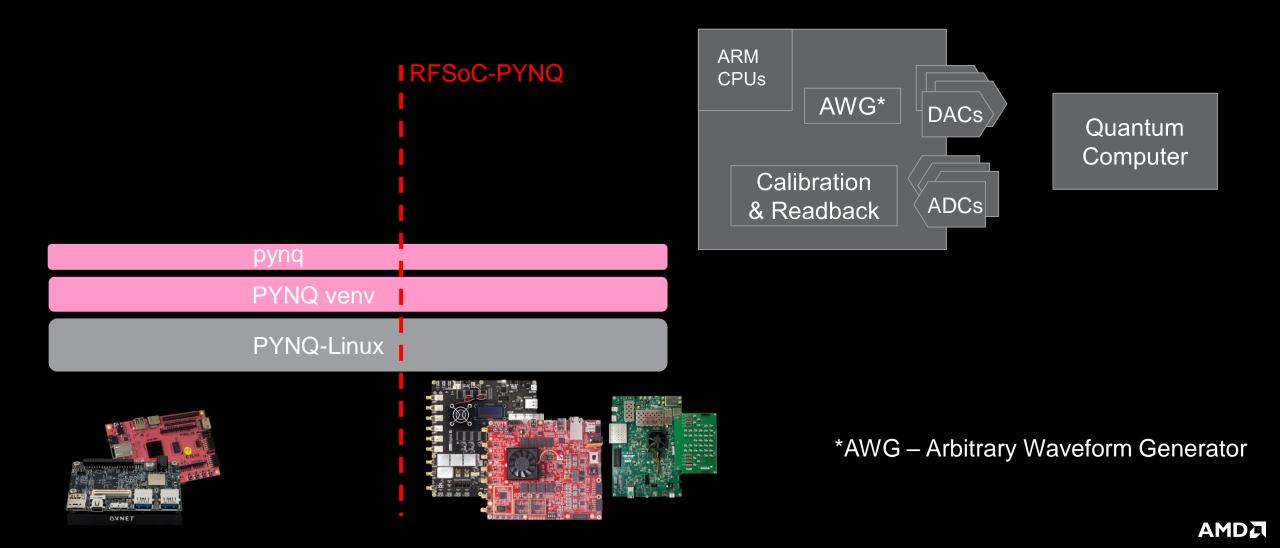

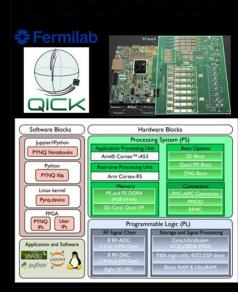

Gustavo Cancelo led a team of Fermilab engineers to create a new compact electronics board: It has the **capabilities of an entire rack of equipment** that is compatible with many designs of superconducting qubits at a **fraction of the cost**.

#### HPCwire.com

📮 openquantumhardware / qick Public

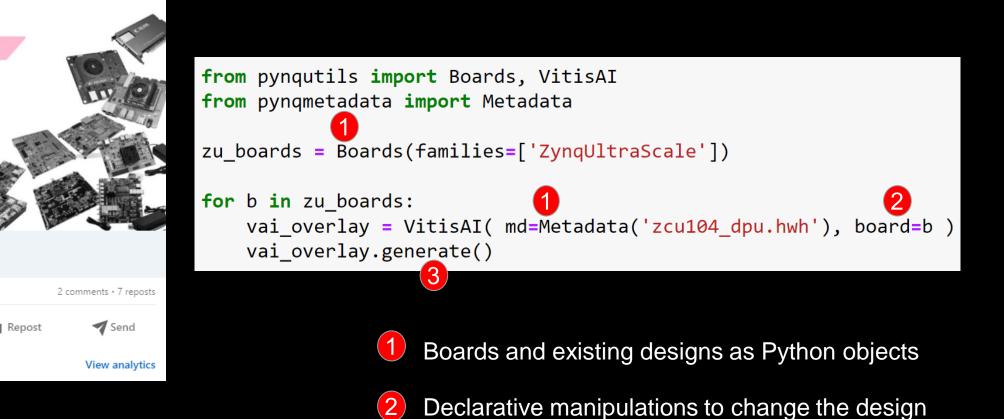

## Coming Soon ... PYNQ-Metadata for Hardware Reuse

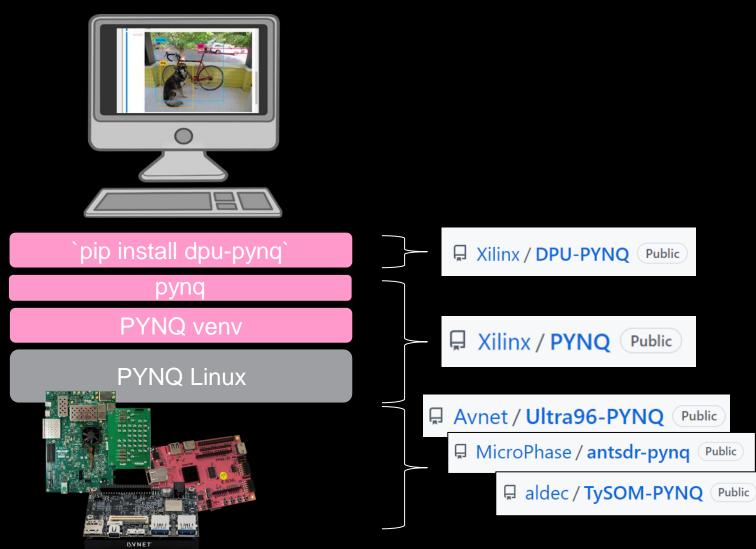

DPU-PYNQ with Vitis AI 2.5 support now available... but more importantly now available on most platforms we could find.

On 20+ boards DPU-PYNQ v2.5.0 release -- now on 20+ boards discuss.pynq.io • 1 min read CCC Cathal McCabe and 122 others 2 comments · 7 reposts CI Repost Like Comment 🚽 Send 5,324 impressions View analytics

Simple backend to reconstruct the design

## Summary

Glue It All Together With Python

Glue Heterogeneous <u>Development and Integration</u> Together with Productivity Frameworks E.g. PYNQ

Nothing shown gets in the way of "High Performance" ... Everything shown is to simplify "Reconfigurable Computing" ... Everything shown is open source, community supported

Please contact me to collaborate on how we can make Reconfigurable Computing more accessible to the HPC community

graham.schelle@amd.com

# Thank you

Please contact me to collaborate on how we can make Reconfigurable Computing more accessible to the HPC community

graham.schelle@amd.com

#