# Fast, Scalable Quantized Neural Network Inference on FPGAs with FINN & LogicNets

@ H2RC at Supercomputing, 2020-11-10

Yaman Umuroglu, Senior Research Scientist Xilinx Research Labs

# Xilinx Research, Dublin

- Established over 14 years ago

- Slowly expanding and increasingly leveraging external funding (IDA, H2020)

- 6 full-time researchers + interns

- Applications & Architectures

- Quantifying the value proposition of Xilinx devices in machine learning

- In collaboration with Partners, Customers and Universities

Lucian Petrica, Giulio Gambardella, Alessandro Pappalardo, Ken O'Brien, Michaela Blott (leader), Nick Fraser, Yaman Umuroglu (from left to right)

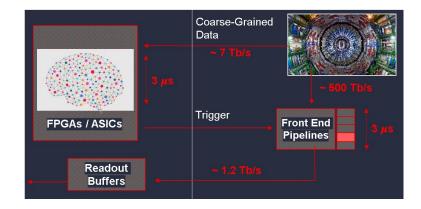

CERN CMS Experiment

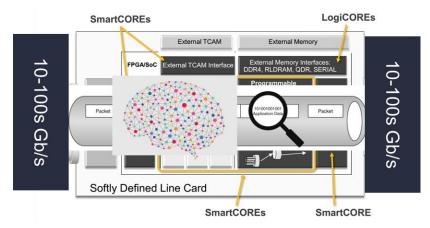

Network Intrusion Detection

- ▶ How do we mix DNNs into *extreme-throughput* applications?

- Need DNNs running at 100Ms of FPS, sub-microsecond latency

## How Efficient Does Your DNN Need To Be? A Spectrum of FPGA Inference Alternatives

less efficient generic broad scope more efficient co-designed specialized

# How Efficient Does Your DNN Need To Be? A Spectrum of FPGA Inference Alternatives

less efficient generic

broad scope

DPU, overlays (10k+ FPS)

FINN (10M+ FPS)

more efficient co-designed specialized

Layer-by-layer compute (Matrix of Processing Engines)

Optimizing compiler/scheduler

Down to 4-bit

Generated heterogeneous streaming architecture

Custom topologies, arithmetic and hardware

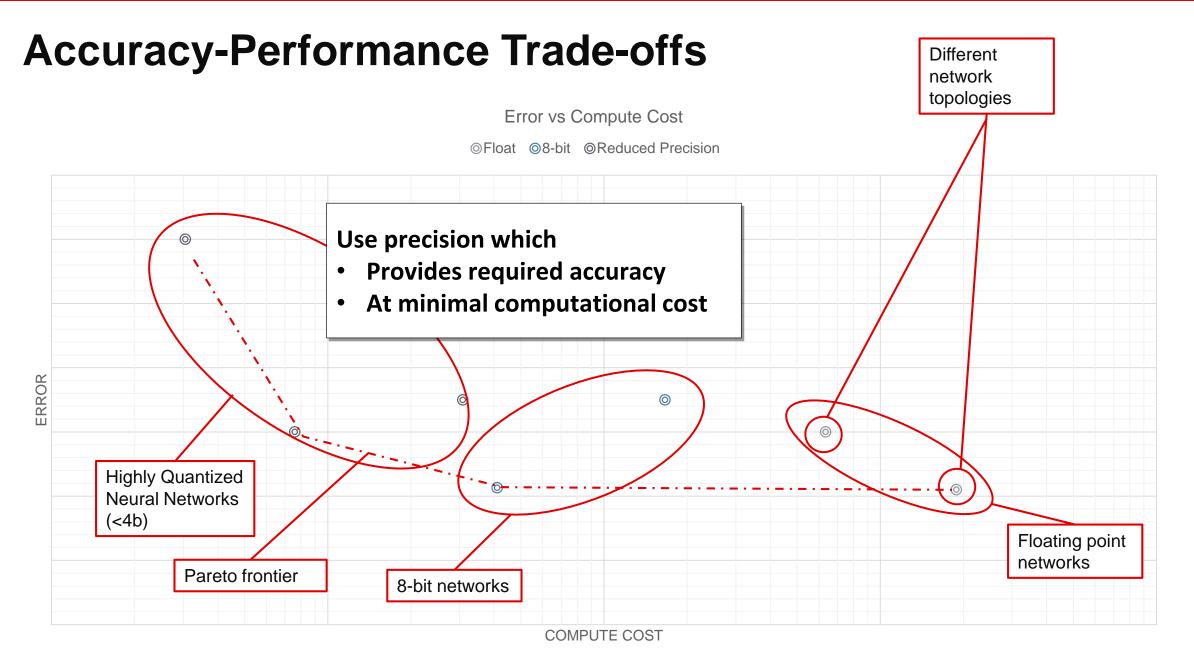

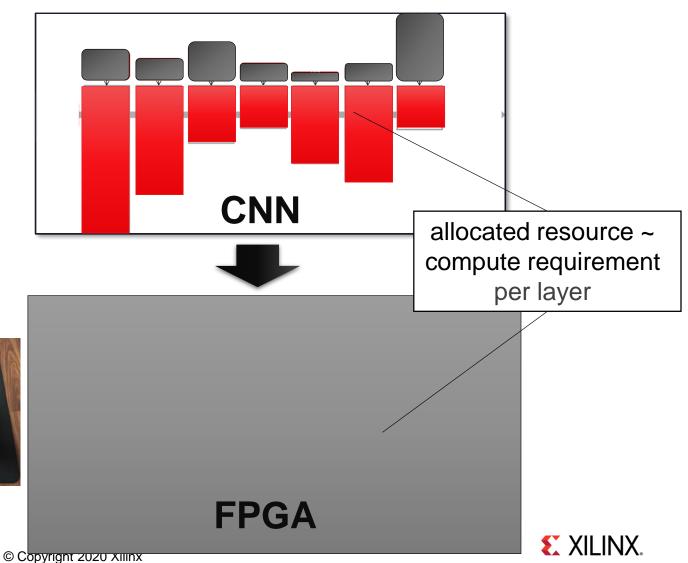

#### **Customization for Efficient Inference**

Customization of Algorithm

Customization of Hardware Architecture

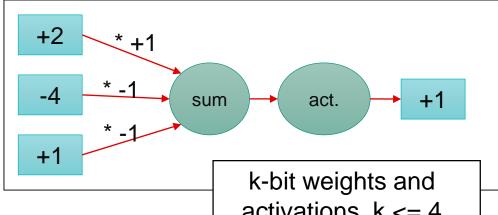

#### Two Key Techniques for Customization

Few-bit weights & activations (tailored to requirements)

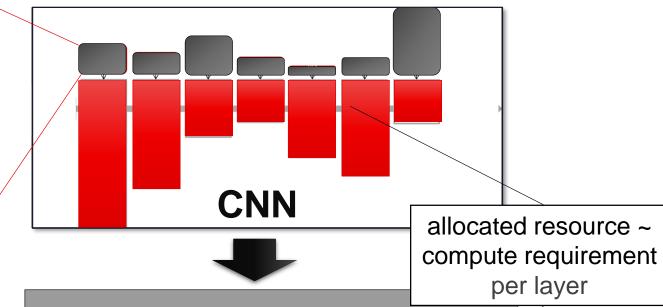

**Streaming dataflow architecture** (tailored to requirements)

activations, k <= 4

keep all on-chip!

© Cop

**FPGA**

per layer

#### Few-bit QNNs + FPGA Dataflow: Showcases

High Throughput & Low Latency

MNIST MLP on ZC706 12.3 M FPS @ 20 W 310 ns latency Low-Power, Real-Time Image Classification

CIFAR-10 CNV on Pynq-Z1 3000 FPS @ 2.5 W 1 ms latency Complex Topologies

ResNet-50 on Alveo U250 2000 FPS @ 70 W 2 ms latency

## The FINN Project: Mission

Support customizing the algorithms with precision, layer types, topologies

Support hardware architecture exploration around dataflow execution

Flexibility on Algorithms

Codesign

on Architectures

**Flexibility**

Transparency and flexibility through open source (if not supported, add your own!)

End-to-end flow to lower adoption barrier

© Copyright 2020 Xilinx

Open source from the ground-up to encourage community contributions

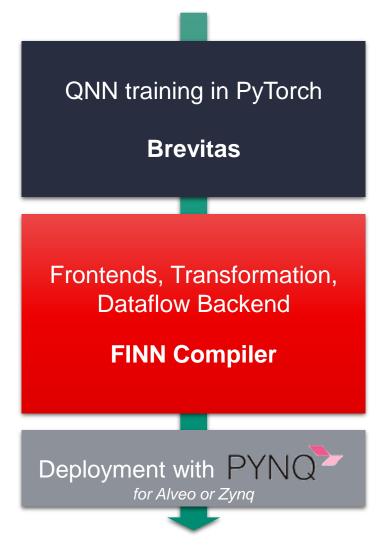

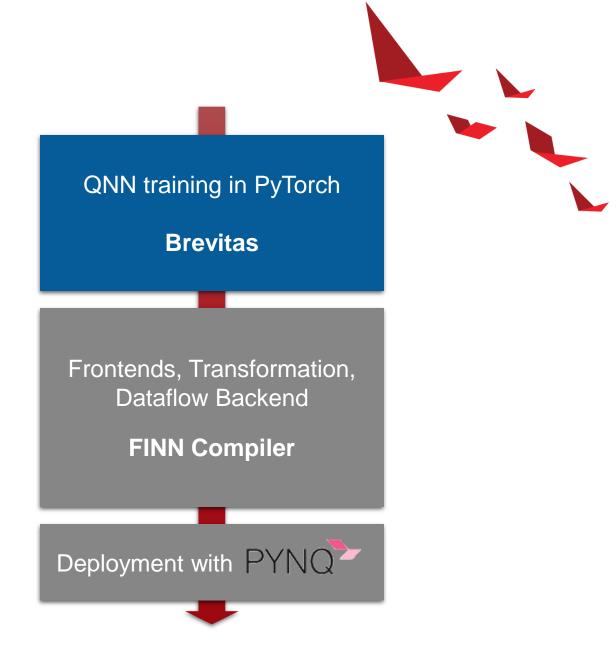

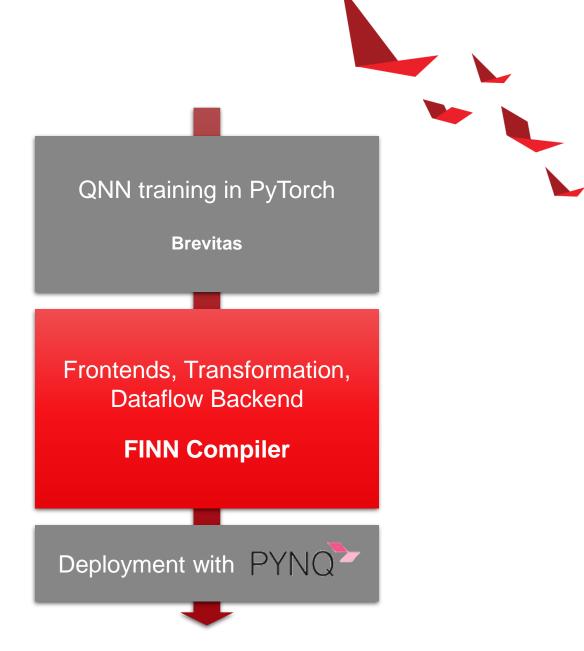

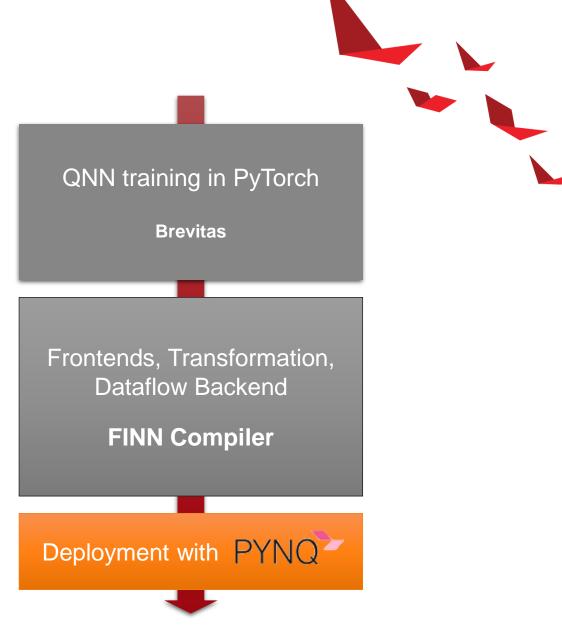

# The FINN Project: Components of the Stack From PyTorch to FPGA

Customization of Algorithm

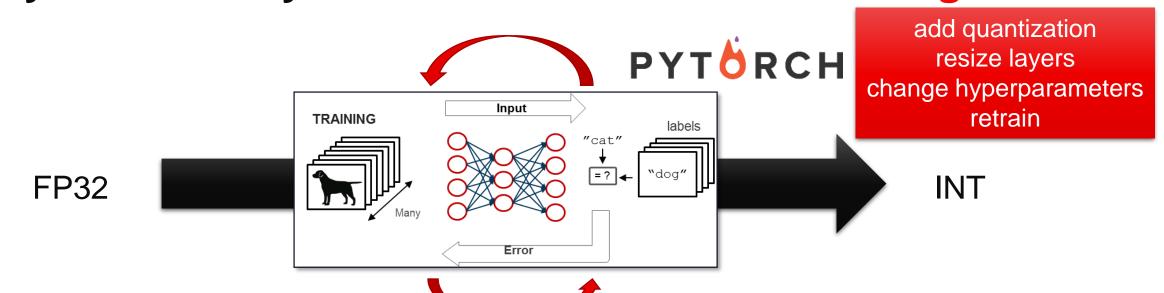

# Quantization-Aware Training in PyTorch with Brevitas

#### **Brevitas:**

#### A PyTorch library for Quantization-Aware Training

#### **Precision**

Preset or learned

Scaling Factors

Granularities,

strategies and

constraints

Target Tensors

Weights,

activations,

cumulators

Loss Function to take HW implementation cost into account

https://github.com/Xilinx/brevitas

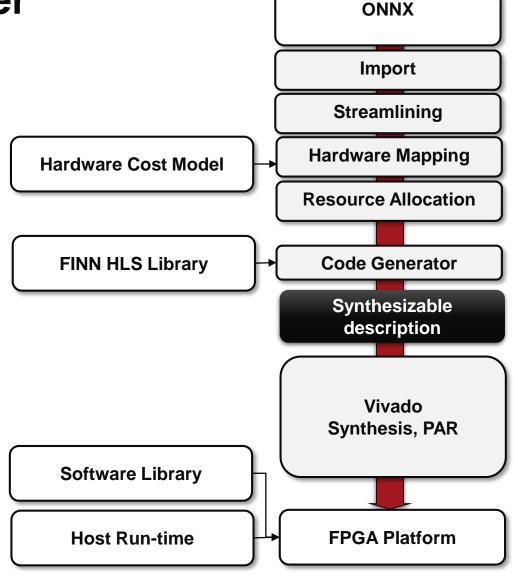

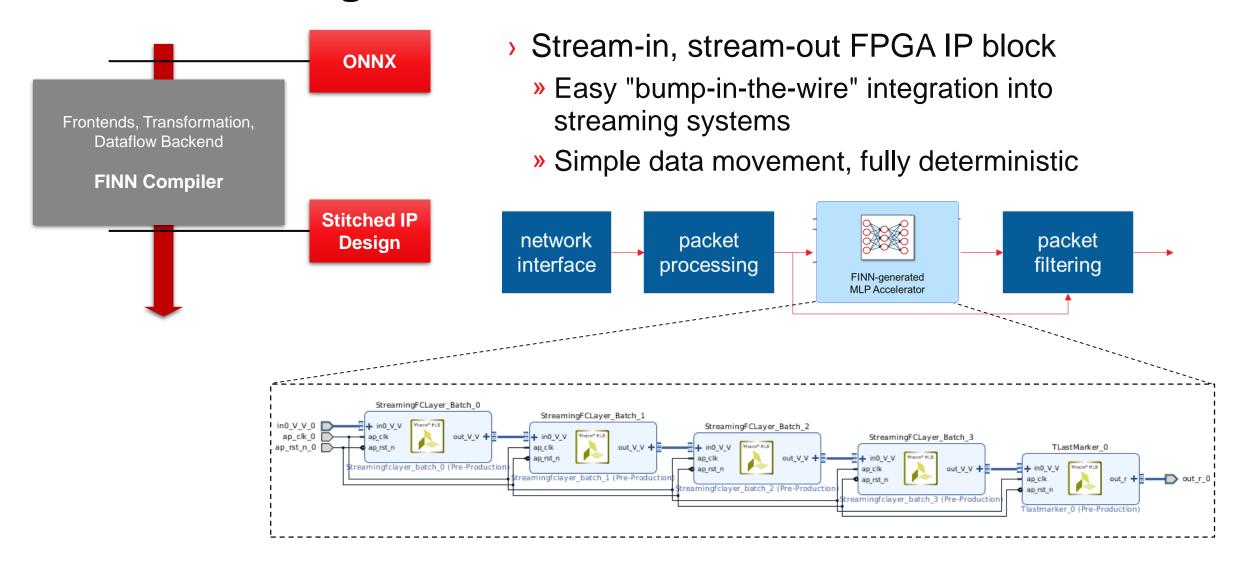

#### Goal of the FINN compiler:

#### Transform QNN into custom dataflow architecture

- Map each layer to HLS description

- Connect with FIFOs/streams

- Stitch together in IPI

## An Overview of the FINN Compiler

- > Python library of graph transformations

- » Each consumes and produces an ONNX graph

- User calls sequence of transformations to create their own flow

- » Example end-to-end flows to get started

```

model = ModelWrapper("fpga4hep-bw%d.onnx" % bw)

model = model.transform(InferShapes())

model = model.transform(FoldConstants())

model = model.transform(GiveUniqueNodeNames())

model = model.transform(GiveReadableTensorNames())

model = model.transform(InferDataTypes())

model = model.transform(Streamline())

model = model.transform(ConvertBipolarMatMulToXnorPopcount())

model = model.transform(absorb.AbsorbAddIntoMultiThreshold())

model = model.transform(absorb.AbsorbMulIntoMultiThreshold())

model = model.transform(RoundAndClipThresholds())

model = model.transform(to_hls.InferBinaryStreamingFCLayer())

model = model.transform(to hls.InferQuantizedStreamingFCLayer())

```

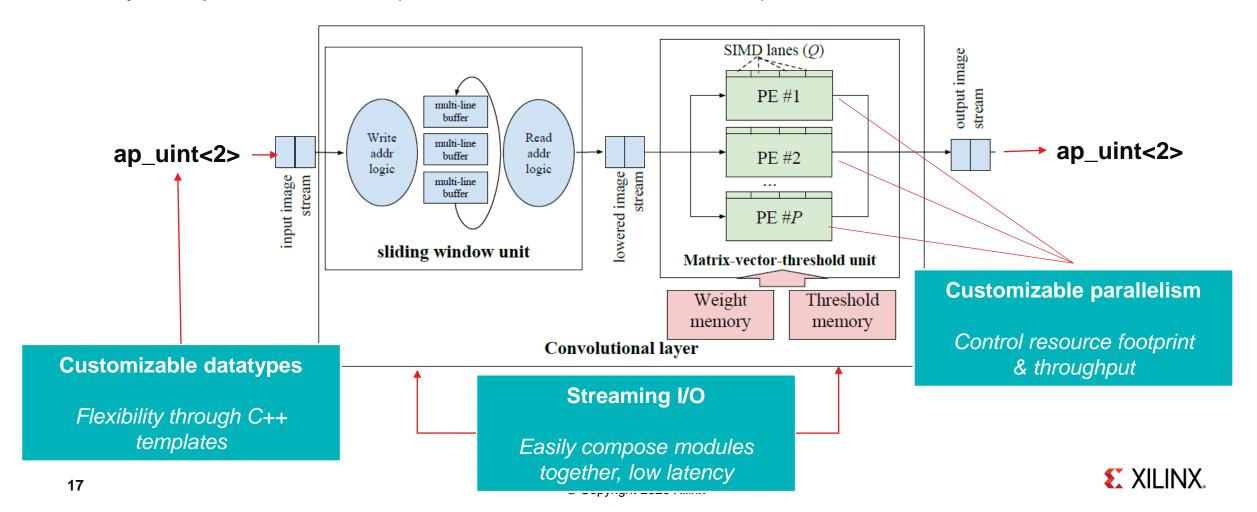

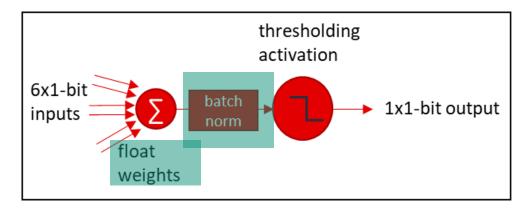

#### The FINN HLS Library

https://github.com/Xilinx/finn-hlslib

- An optimized, templated Vivado HLS C++ library of 10+ common DNN layers

- Key component: MVTU (Matrix Vector Threshold Unit)

#### How does the generated architecture look?

# Deployment with PYNQ

# Deployment with PYNQ for Python Productivity

```

# numpy.ndarray shapes for i/o

ishape packed = (1, 49, 2)

oshape packed = (1, 1, 40)

# set up the DMA

dma.sendchannel.transfer(in buf : numpy.ndarray)

dma.recvchannel.transfer(out buf : numpy.ndarray)

# wait until all transfers complete

dma.sendchannel.wait()

dma.recvchannel.wait()

```

- Use PYNQ-provided Python abstractions and drivers

- User provides Numpy array in, calls driver, gets Numpy array out

- Internally use PYNQ DMA driver to wr/rd NumPy arrays into I/O streams

https://github.com/Xilinx/PYNQ https://github.com/Xilinx/Alveo-PYNQ

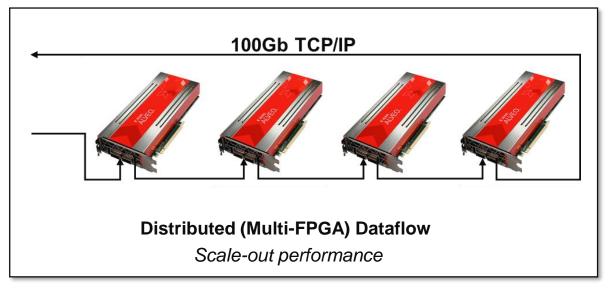

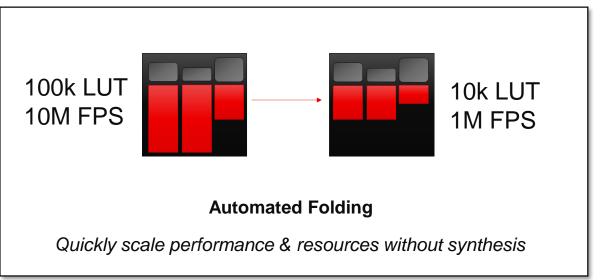

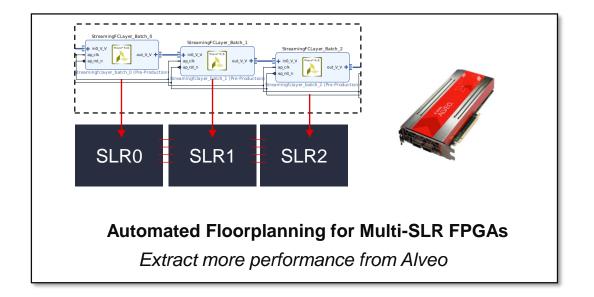

## **Upcoming FINN Features**

# LogicNets

# How Efficient Does Your DNN Need To Be? A Spectrum of FPGA Inference Alternatives

LUT LUT LUT

less efficient generic broad scope

**DPU**, **overlays** (10k+ FPS)

**FINN** (10M+ FPS)

**LogicNets** (100M+ FPS)

more efficient co-designed specialized

Layer-by-layer compute (Matrix of Processing Engines)

Optimizing compiler/scheduler

Generated heterogeneous streaming architecture

Custom topologies, arithmetic and hardware

The DNN is the circuit

Fully unfolded, pipelined, feedforward datapaths

#### LogicNets at a Glance

convert

LUT LUT

Specialized DNN Topology

(with high sparsity + activation quantization)

Fully-Spatial Circuit Implementation

one full sample every clock low logic depth, high  $F_{clk}$  100M's of samples per second

**PyTorch**

**FPGA**

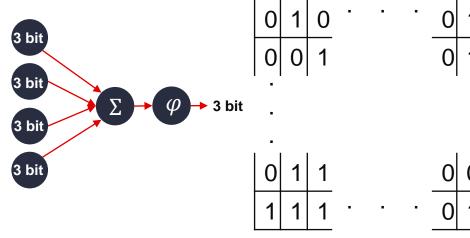

## **Key idea: Quantized Neurons as Truth Tables**

Neuron Equivalent (NEQ)

Hardware Building Block (HBB)

convert (enumerate inputs)

Total input: 6 bits Total output: 1 bit

Hardware cost: 1 x LUT6

**PyTorch**

**FPGA**

Total input: 6 bits

Total output: 1 bit

## **Prohibitive Cost of Implementing Large Truth Tables**

Total input: 12 bits

Total output: 3 bit

Co-design DNN topology to avoid intractably large LUTs: high sparsity + few-bit activations

LUT6 cost of the neuron:

~4095 LUT6s

Truth Table Size:  $4096 \times 15 = 2^{3*4} \times 3*5$

#### LogicNets Key Results

hls4ml JSC dataset [Duarte et al.]

**Jet Tagging (CERN LHC)**

~72% accuracy

using ~38k LUTs

at 427 M samples / second

with 13 ns latency

UNSW-NB15 Network Intrusion Detection dataset [Moustafa et al.]

#### **Network Intrusion Detection**

~91% accuracy

using ~16k LUTs

at 471 M samples / second

with 9 ns latency

'Umuroglu et al., Preprint:

#### Conclusion

#### **FINN**

- QNN solution stack from training to custom dataflow architecture

- Full co-design environment with growing library examples

- Flexible, customizable open-source compiler framework

#### LogicNets

- Sparse + quantized topology converts directly to LUT circuit

- Many exciting future research directions

- To be open-sourced as part of FINN ecosystem (~Q1 2021)

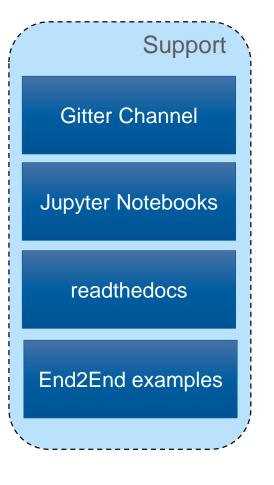

## Join our Growing Open-Source Community!

https://xilinx.github.io/finn

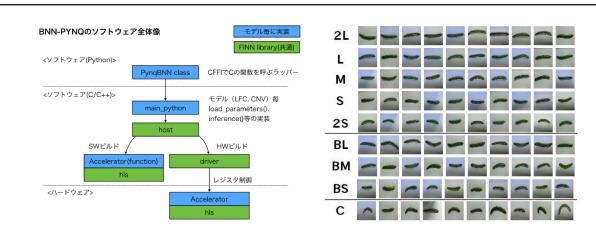

University courses, student/hobbyist projects

Japanese documentation effort + «cucumber sorting»

Sketch Recognition (Xilinx Edinburgh)

# Thank You