# Accelerating Intelligence

John D. Davis, Ph.D.

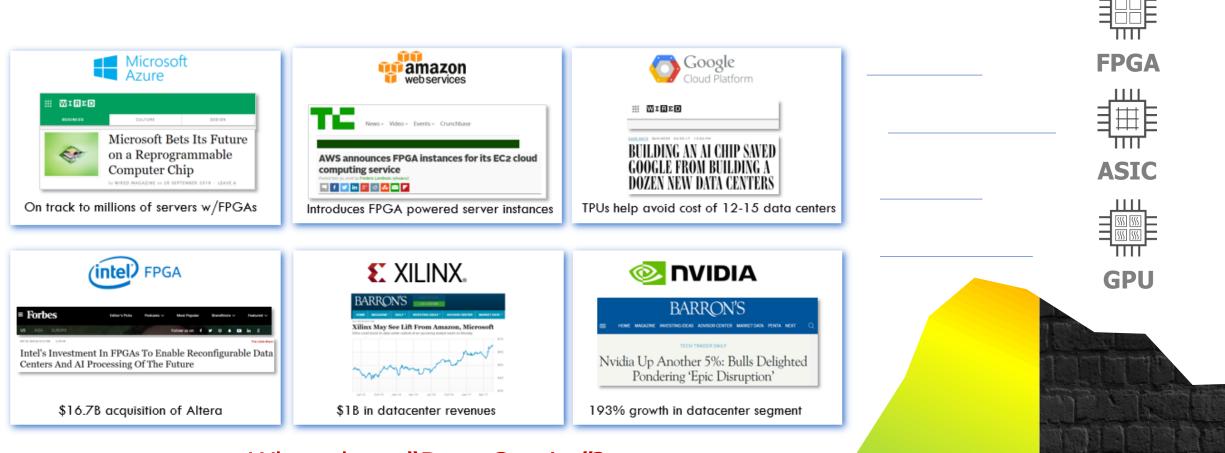

## Hardware Accelerators Break Through the Processing Wall

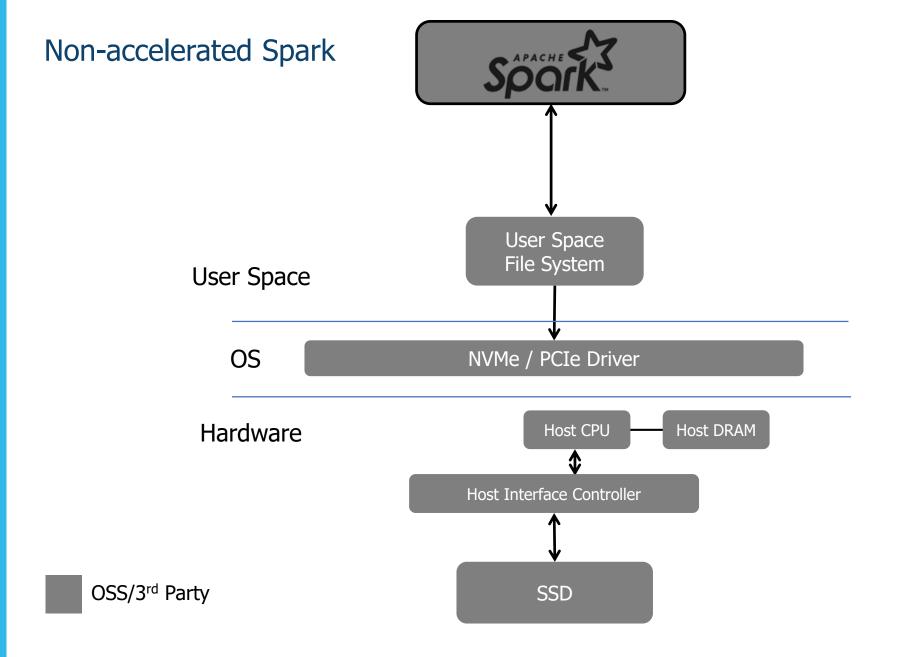

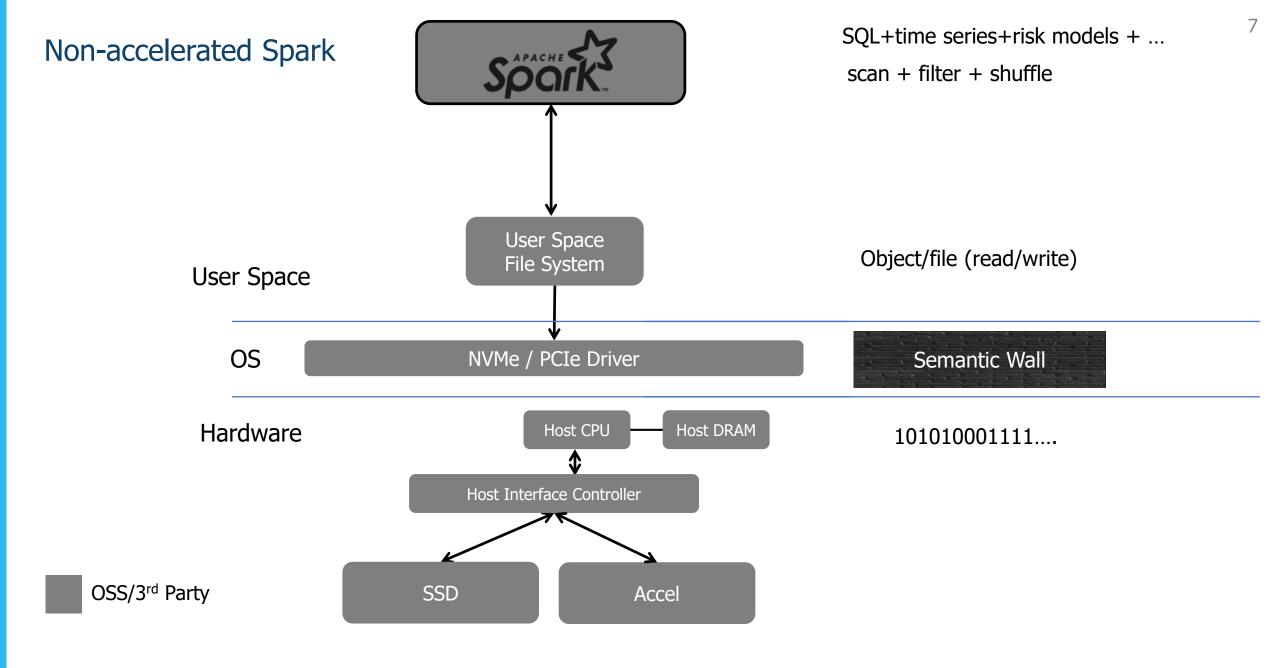

### What about "Data Gravity"? Push compute near the Data

Bigstream Confidential © 2018

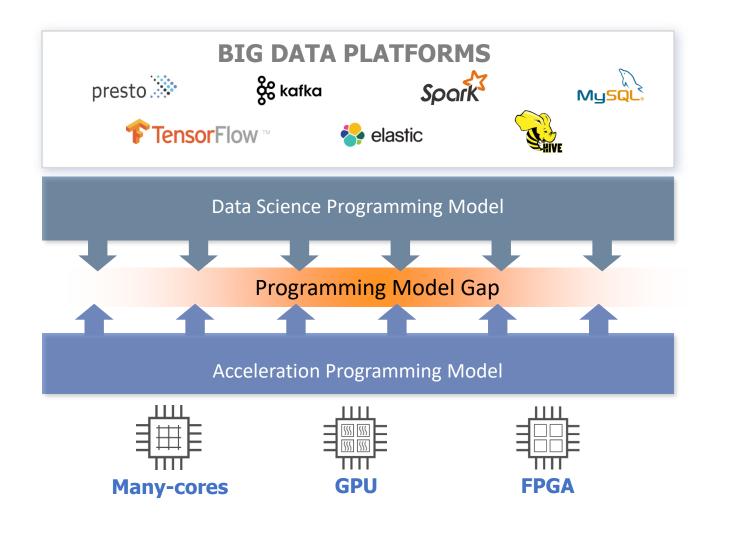

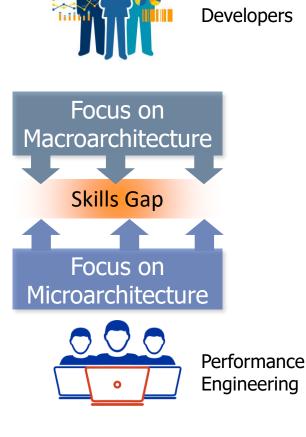

## Inhibitor: Programming Model Gap for Hardware Accelerators

🙈 bigstream

Data Scientists &

Bigstream Confidential © 2018

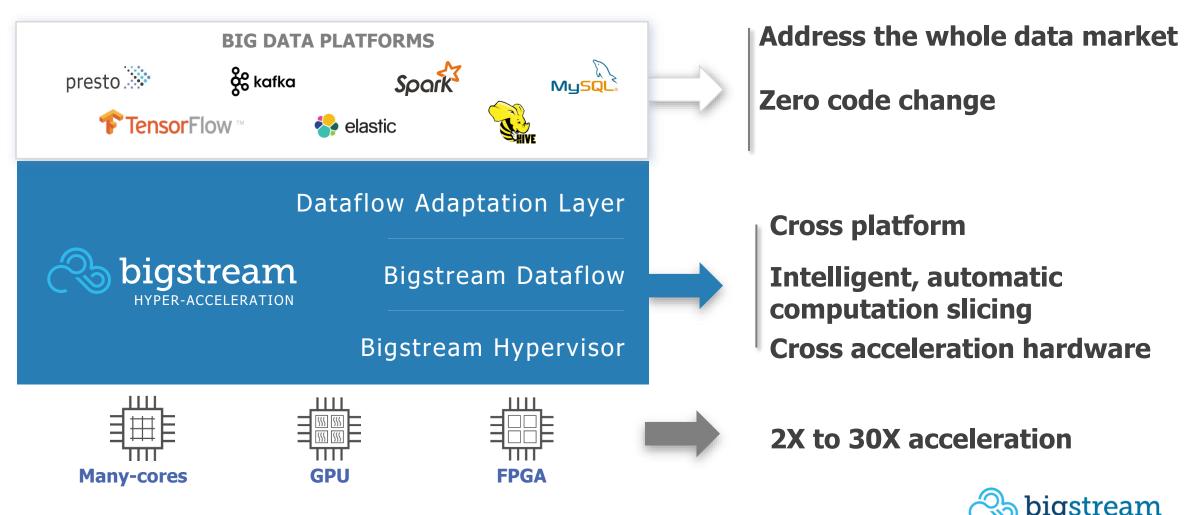

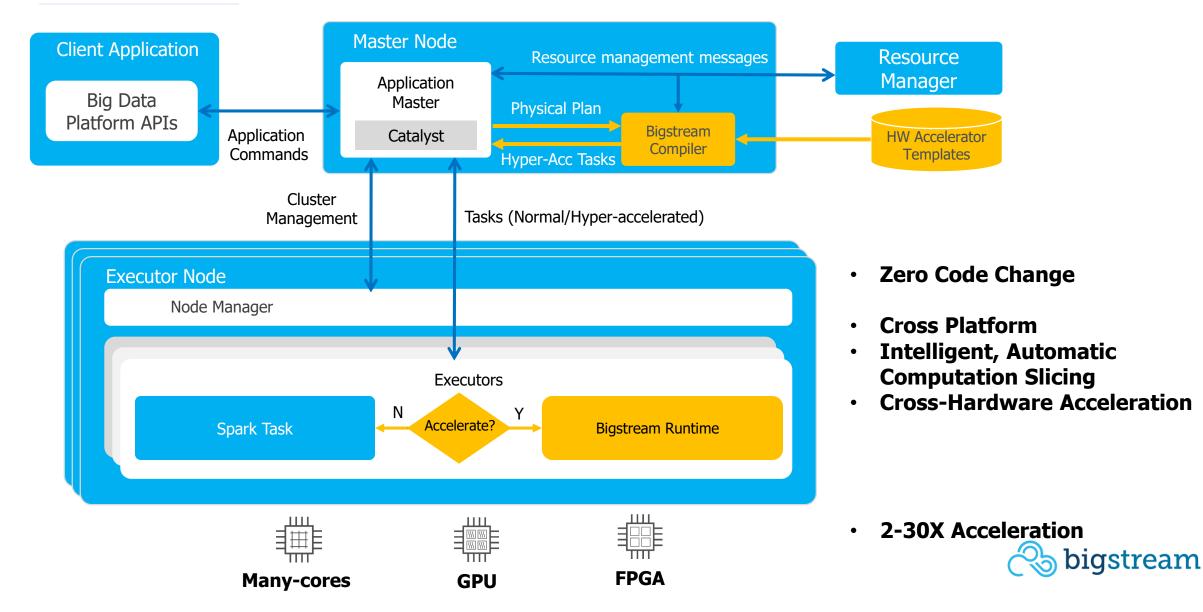

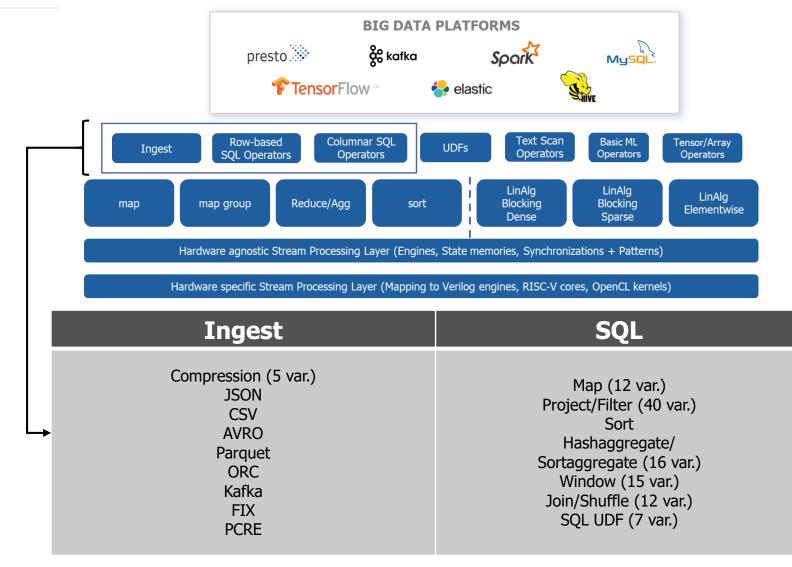

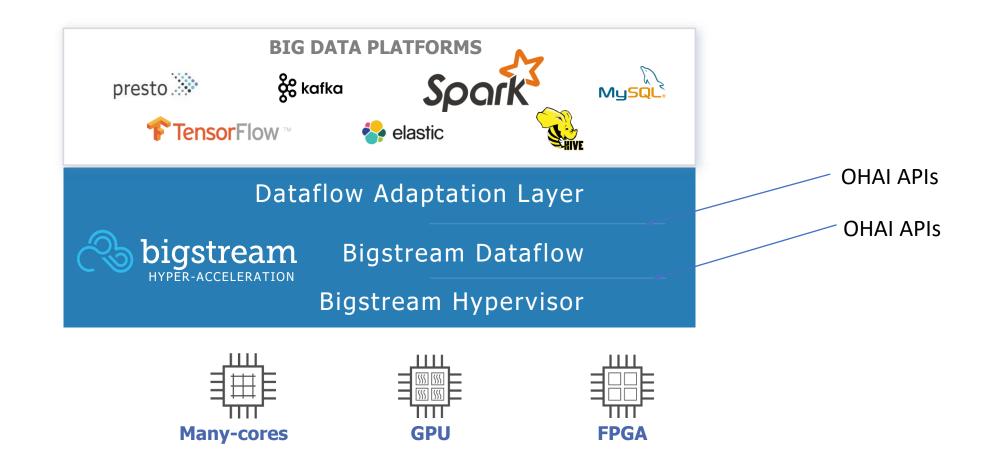

## Introducing: Bigstream Hyper-acceleration Layer

Goal: Provider of Open-ecosystem for Hyper-acceleration

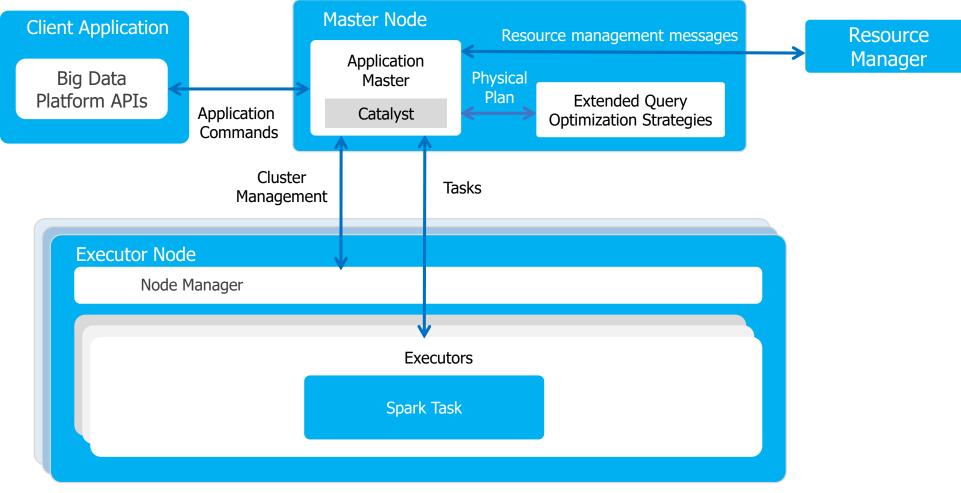

## Apache Spark

Many-cores

Bigstream Confidential © 2018

## Bigstream Seamless Acceleration of Apache Spark

## Hyper-Acceleration Layered Compilation Approach

### HW Accelerator Engines

| Deserialization<br>Decompression | JSON                                   | (.*) s   | Search/Regex                | PCRE (3rd Party)               |

|----------------------------------|----------------------------------------|----------|-----------------------------|--------------------------------|

|                                  | CSV<br>Parquet (under development)     |          | <b>CPU</b> Cores            | RISC-V (3 <sup>rd</sup> Party) |

|                                  | FIX (under development)                | °⁄°°     | Machine<br>Learning         | Linear/Logistic<br>Regression  |

|                                  | Snappy<br>GZIP (3 <sup>rd</sup> Party) |          |                             | K-means                        |

| Encryption/<br>Decryption        | AES                                    |          | Deep                        | CNN (3 <sup>rd</sup> Party)    |

| SQL                              | Project                                | Learning | RNN (3 <sup>rd</sup> Party) |                                |

|                                  | Filter                                 |          | Networking                  | IP/UDP                         |

|                                  | Sort<br>Hash Aggregate                 |          |                             | IP/TCP (3 <sup>rd</sup> Party) |

Bigstream Confidential © 2018

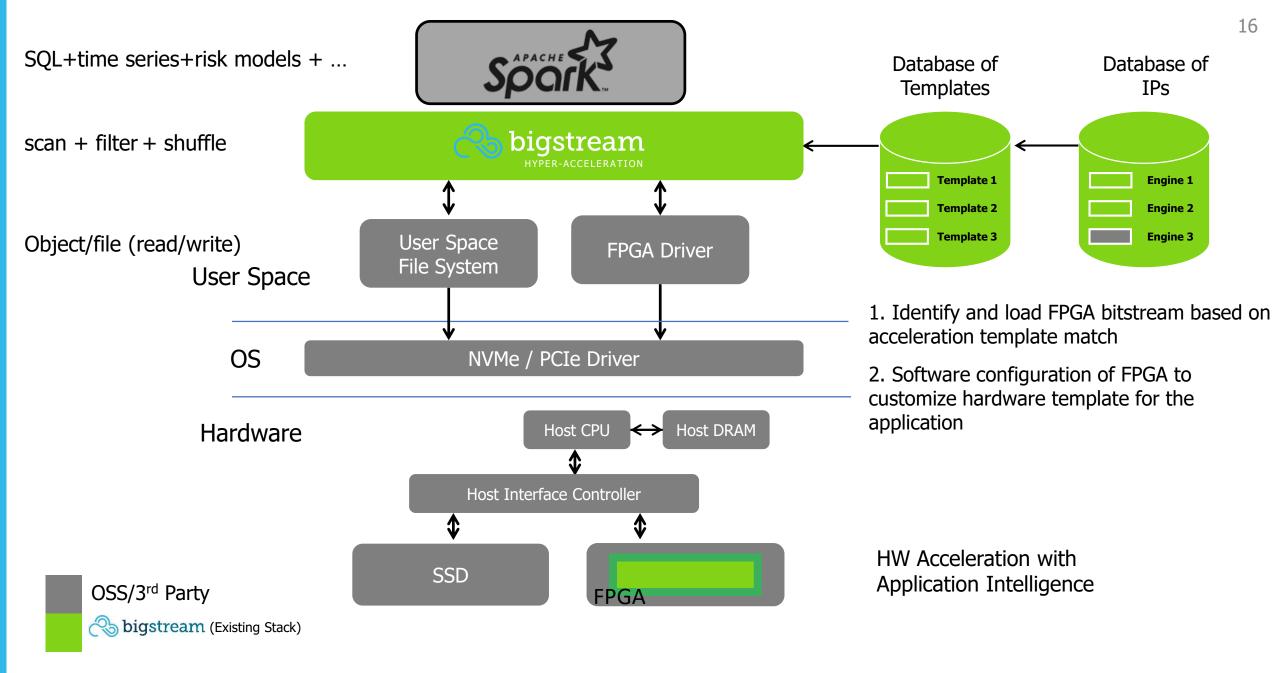

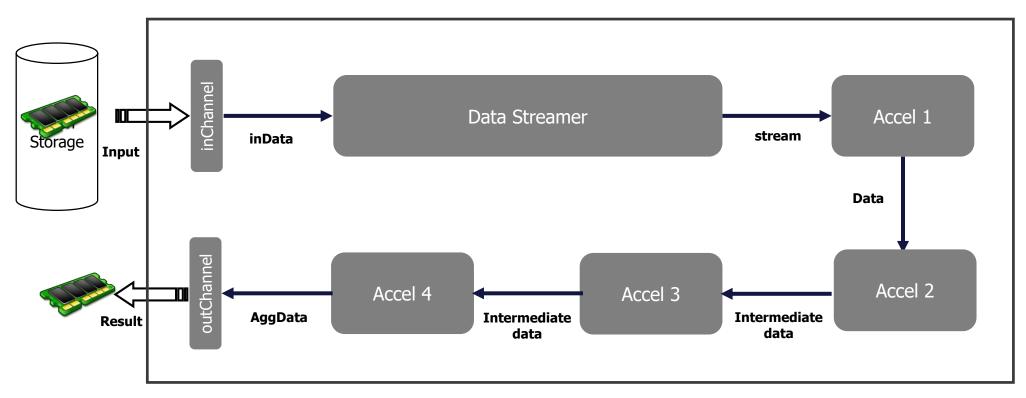

## General Application and HW Characteristics

### • Application characteristics:

- Batch and streaming analytics applications

- Collection of computation/transformation stages

- Terabytes to Petabytes or more of data

- Large clusters: 10's 10,000's servers

- I/O (network and/or storage) and compute bound

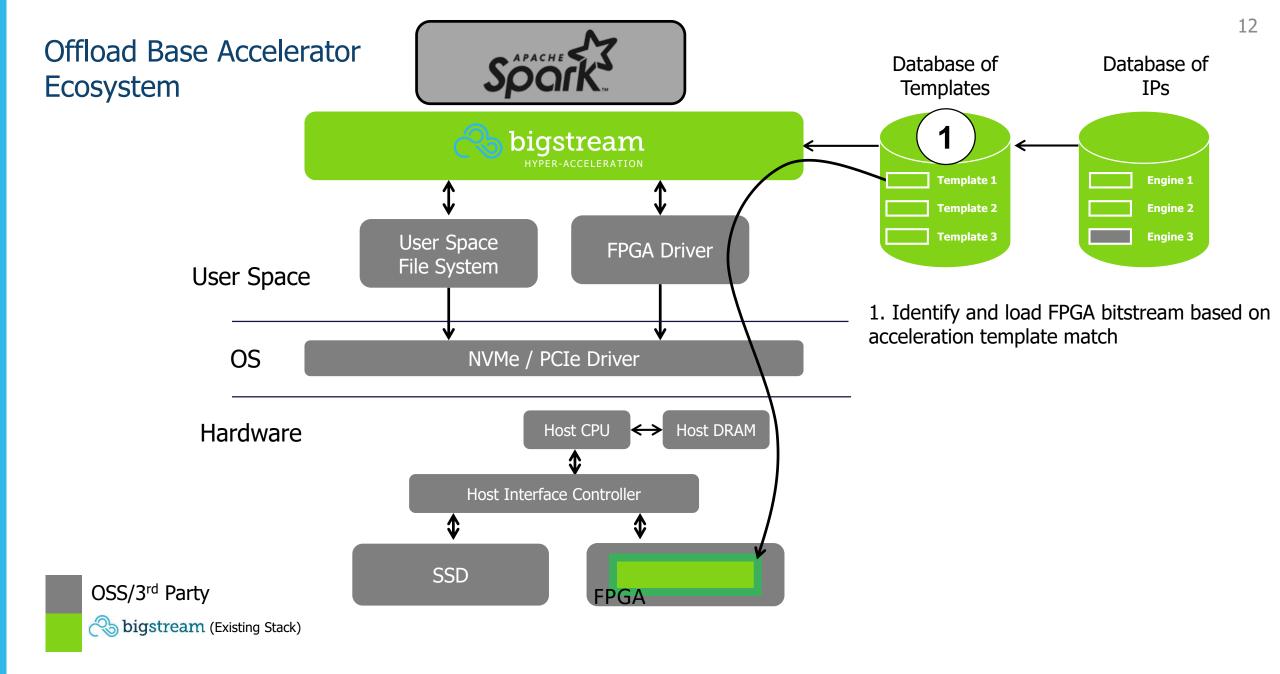

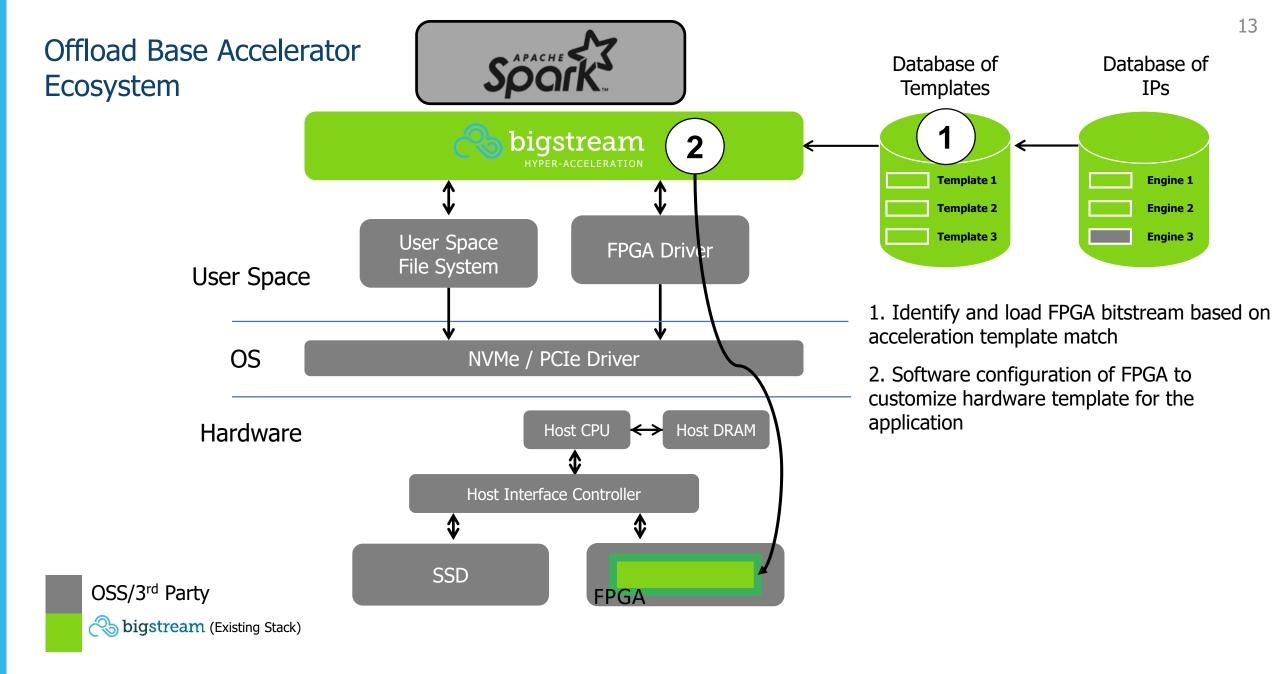

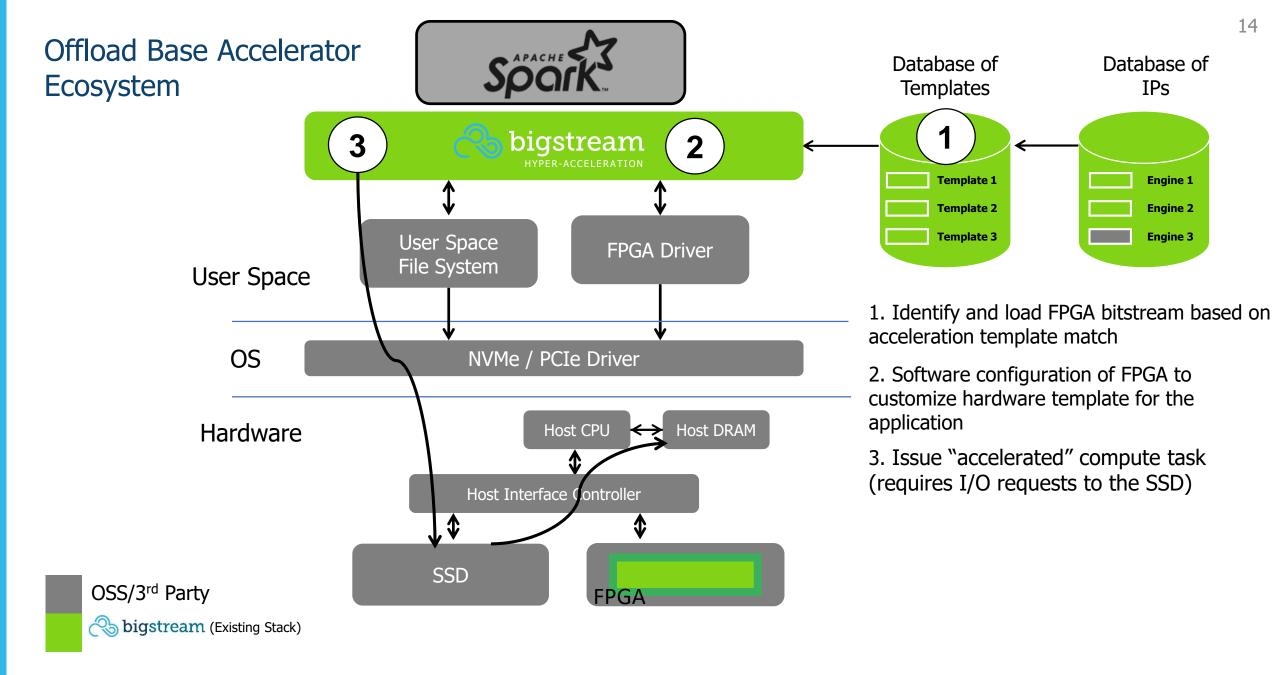

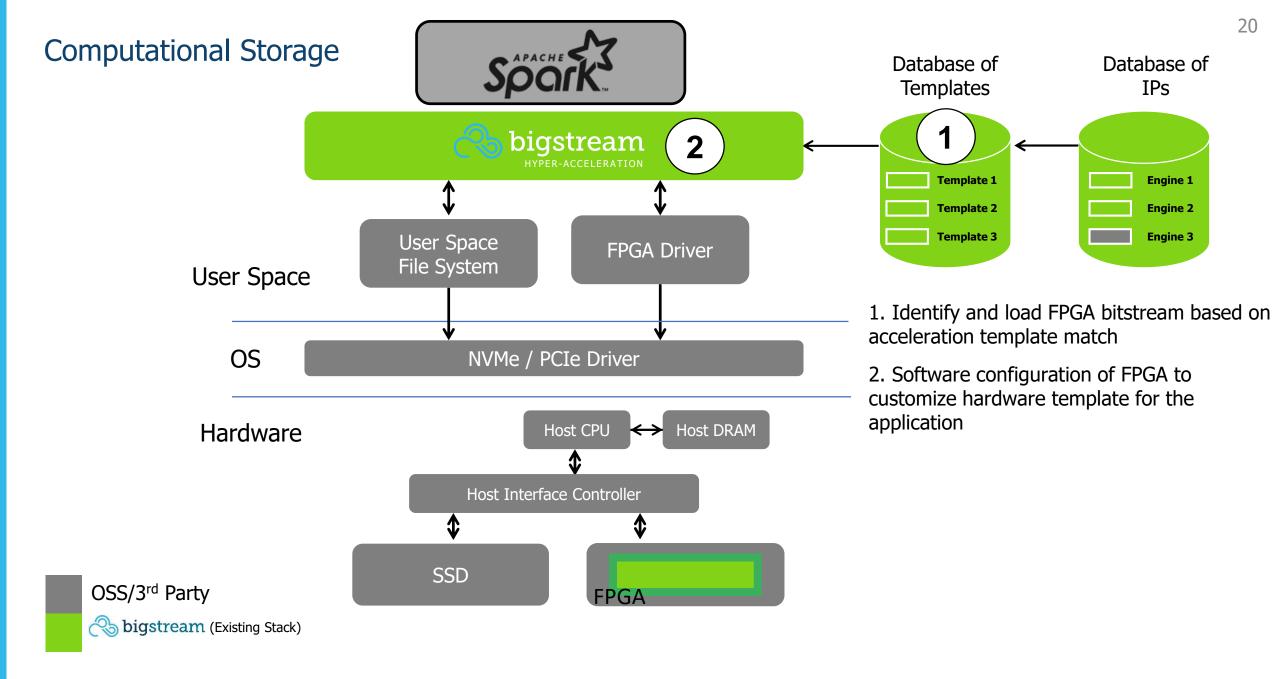

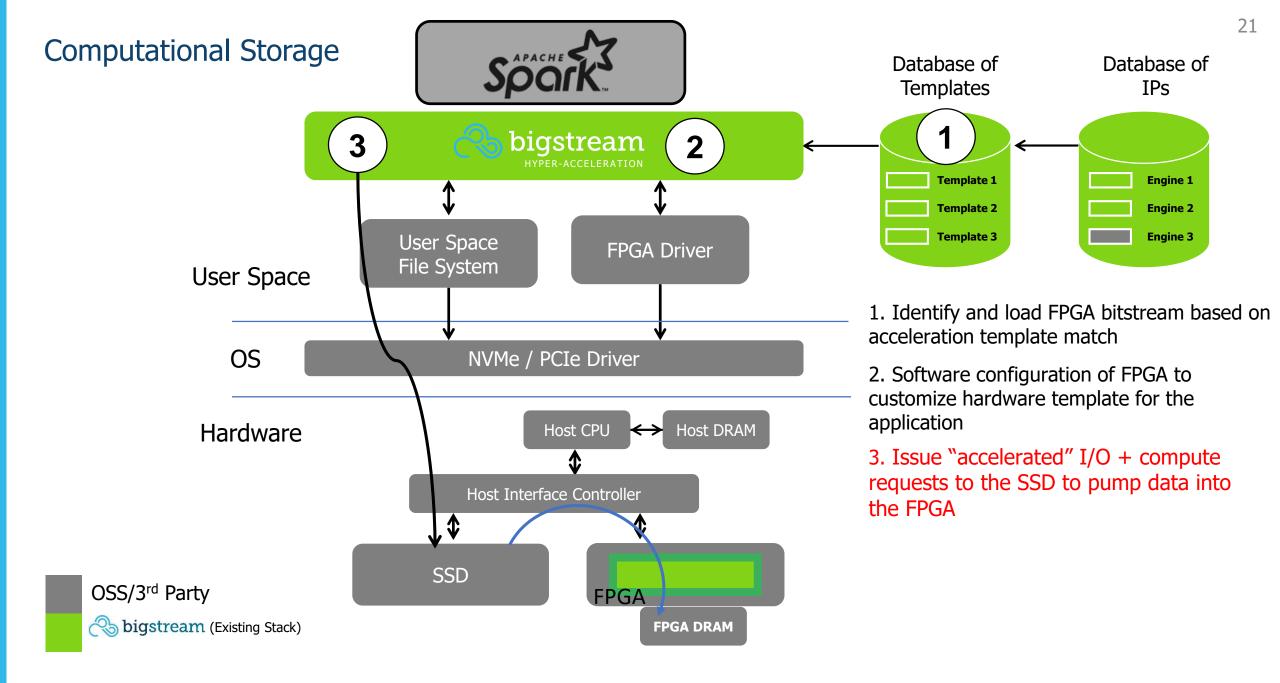

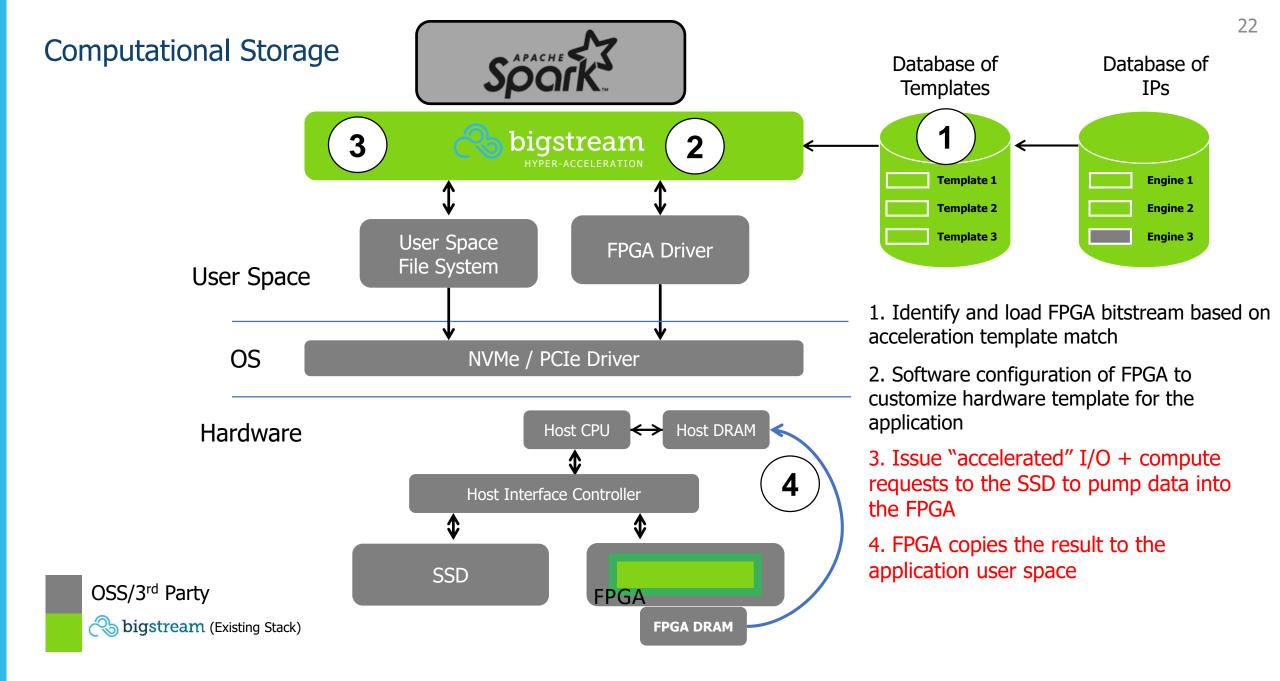

### • How we use the FPGA:

- Build out pipelines and import as kernels

- Computational overlays (Time Division Multiplexing)

- Offload and Inline (Storage and Network) acceleration

- Moving between Streaming, Memory Mapped, and P2P DMA with Software

- Bringing Computation to the Data.

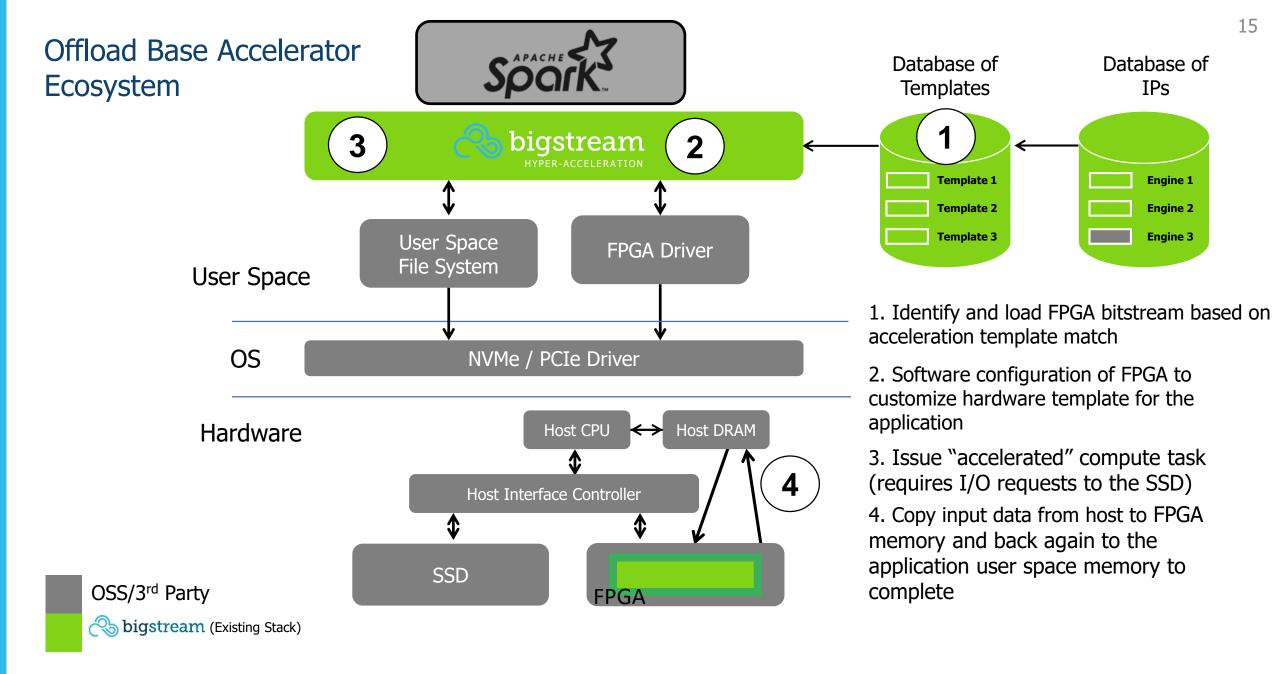

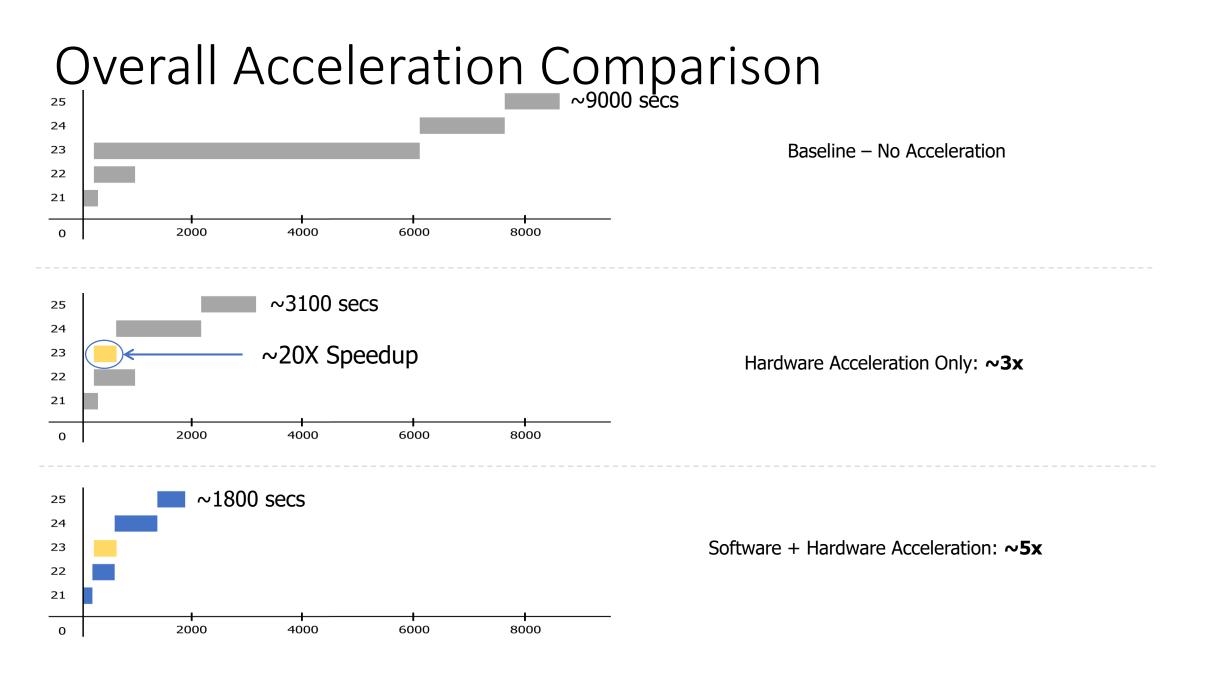

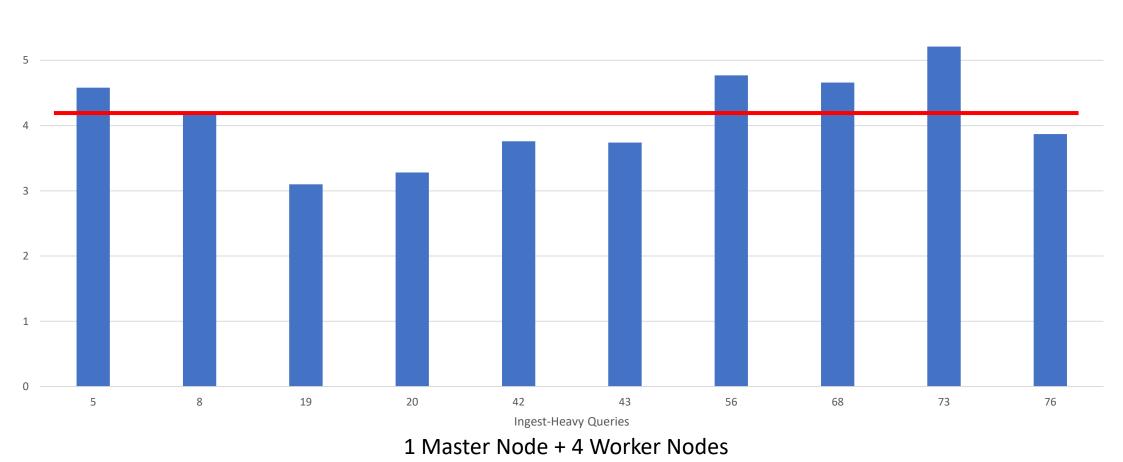

## Offload Performance: 5 Node Cluster

TPC-DS SpeedUp

Spark baseline vs FPGA acceleration with Zero Code Change

## •Rewind for Computational Storage

# • Memory-mapped DMA

// Read from SSD part

buffer = (char\*) **malloc** (size);

bytes read = **fread**(buffer, 1, size, fd);

//WRITE PART- from host to fpga

err = clEnqueueWriteBuffer(commands, buffer, CL\_TRUE, 0, (data\_actual\_size + 96), json\_write\_host\_mem, 0, NULL, & write\_event);

clWaitForEvents(1, & write event);

//Actual compute task

err = clEnqueueTask(commands, kernel, 0, NULL, & kernel\_event);

clWaitForEvents(1, & kernel\_event);

//READ PART - from fpga to host

#### err |= clEnqueueReadBuffer(commands, json\_data\_ptr, CL\_TRUE, s\_read\_offset, bytes\_to\_read + 32, son\_read\_host\_mem, 0, NULL, & readevent2);

#### > P2P DMA

// Read from SSD & write to fpga

**clCreateBuffer**(context[1], CL MEM READ ONLY | CL MEM EXT PTR XILINX, (aligned\_size), & xmem\_flags, & err); \_mapped\_virtual\_addr = **clEnqueueMapBuffer**(commands, d\_axi00\_ptr0\_wr, CL\_TRUE, CL\_MAP\_READ | CL\_MAP\_WRITE, 0, (aligned\_size), 0, NULL, & map\_event, & err); clWaitForEvents(1, & map\_event); bytes read = **read**(\_fd, ((char \*) \_mapped\_virtual\_addr), size); //Actual compute task err = CIEnqueueTask(commands, kernel, 0, NULL, & kernel\_event); clWaitForEvents(1, & kernel\_event); //READ PART -from fpga to host err |= **CIEnqueueReadBuffer**(commands, json\_data\_ptr, CL\_TRUE,

s read offset, bytes to read + 32, son read host mem, 0, NULL, & readevent2);

### Same code can run in VU9P+ and ZU19, just change the target device

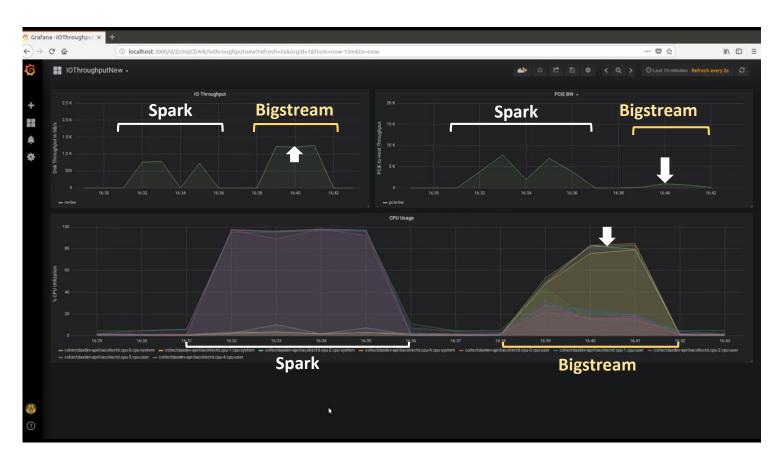

## P2P Comparison

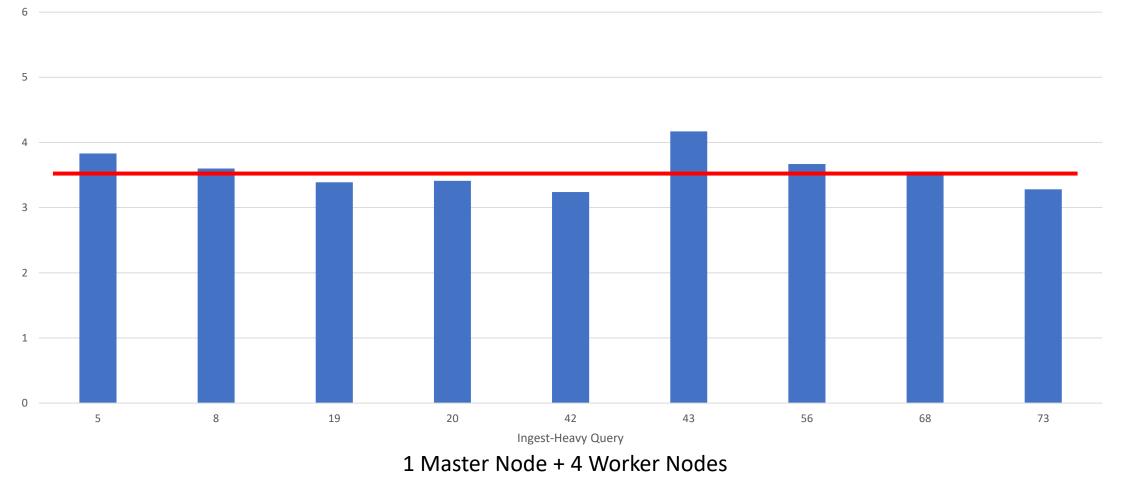

- SmartSSD (SSD + FPGA)

- 45% Utilization (BRAM, LUTs, DSPs)

- System level results 6c Xeon Workstation

- Spark vs P2P DMA

- Single FPGA, FPGA Pooling, & Clusters of FPGAs

- TPC-DS with 340 GB to 2.7 TB

- Up to 2 SmartSSDs/server

- 5 node cluster (1 master node and 4 worker nodes)

# System-Level Results

- Row-based engine with TPC-DS queries

- Lower CPU utilization and fewer cores

- Higher device I/O bandwidth

- Lower host PCIe bandwidth

- Reduced CPU DRAM Utilization

- Opportunities

- Not all DMAs are the same.

- Flexibility to mix and match DMA

- When to use P2P?

## P2P Performance: 5 Node Cluster

6

TPC-DS SpeedUp

Spark baseline vs FPGA acceleration with Zero Code Change

### Accelerators Everywhere!

**FPGA**

## **Open Hyper-Acceleration Initiative**

- Goal: Extend the development community around hyperacceleration

- Enable different developers from completely differently skill set

- HW Template and engine developers

- HW platform developers (add new FPGAs and FPGA cards)

- Add new Platforms (i.e., Presto, Hive, TF, etc.)

- Invitation only contributions at this time

- If interested, please come talk to me

# OHAI Open APIs

## Conclusions

### • Flexibility

- Accelerating more than just compute: moving compute to the data vs. data to compute

- Programmability

- Time division multiplexing/hardware overlays

- Software and Hardware configuration

- Generality

- Combining HW and SW acceleration transparently embedded in Big Data Platforms

- Automatically

- Bigstream Hyper-Acceleration with Zero Code Change

# Thank You

John D. Davis, Ph.D. john@bigstream.co